В попередніх темах, при розробці нашого проекту "Binary to BCD converter", ми вже розглянули як буде компілюватися проект, а також як він буде синтезований в доступні для MAX+plusII та Quartus II серії CPLD та FPGA. І при цьому дізнались на скільки ефективно компілятор упаковує наш проект в мікросхему(маю на увазі CPLD або FPGA), тобто скільки ЛБ займає проект при зміні параметрів (стилів) синтезу(Fast, Normal, WYSIWYG в MAX+plusII ). Тепер давайте проведем симуляцію проекту і подивемось як буде вести себе схема при зміні параметрів синтезу вже відомих нам ( Fast, Normal, WYSIWYG в MAX+plusII ), але спочатку добудемо ідеальний варіант симуляції нашого проекту щоб мати з чим порівнювати, тобто створимо ідеальні умови синтезу тобто не будемо враховувати затрики елементів схеми. До початку симуляції створимо в WaveForm Editor'i часову діаграму тобто файл з розширенням *.scf вставимо в діаграму порти вводу і виводу і на порти вводу( по схімі В0... В7) виставимо деякі вхідні дані(стимули) відносно яких буде проводитись симуляції схеми. Для того щоб просимулювати схему в ідеальному варіанті без затримок нам потрібно відкрити вікно компілятора Compile, далі вибрати закладку Processing, і поставити галочку навпроти Functional SNF Exctractor як на рисунку 1.

Рис. 1

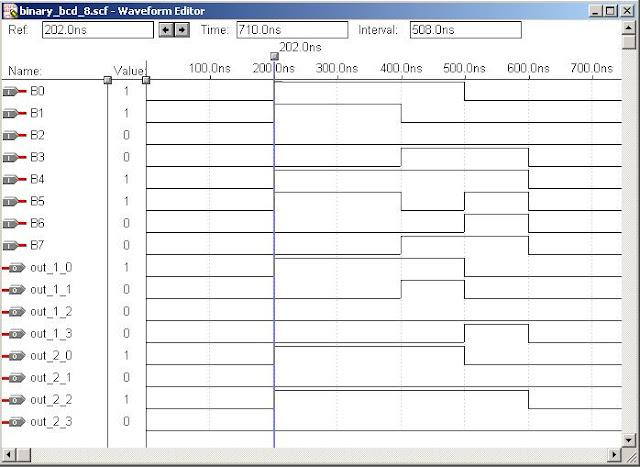

Перейти до вікна компілятора і провести компіляцію проекта. Далі переходимо до вікна Simulator, і проводимо симуляцію проекта при натисканні на кнопку Start, далі відкриваємо результат симуляції маємо отримати щось на подобі рисунка 2.

Рис. 2

Отже ми отримали ідеальний варіант симуляції нашої схеми. І як кажуть на крутих телеканалах "залишайтесь з нами, далі буде ще цікавіше". А тепер проведемо симуляцію з врахуванням затримок між елементами схеми і прицьому будемо змінювати параметри (стилі Fast, Normal, WYSIWYG в MAX+plusII ) синтезу проекту і кожен раз при зміні параметрів будемо перекомпільовувати проект. Перед зміною стилів вийдемо із режиму функціональної симуляції тобто знімемо галочку в закладці Processing/ Functional SNF Exctractor як на рисунку 3. І поставимо галочки навпроти : Timing SNF Extractor, Optimize Timing SNF(не обовязково).

Рис. 3

Рис. 4 Стиль Fast.

Рис. 5 Стиль Normal

Рис. 6 Стиль WYSIWYG

Виходячи із результатів симуляції ми отримали часові діаграми симуляції схеми із врахуванням затримок елементів схеми при перехідних процесах (при зміні вхідних стимулів) все це видно із рис.4, рис. 5, рис. 6 де червоним обведено як поводиться схема при перехідних процесах, і тут я згадав свого викладача коли навчався в інституті, який розказував про "гонки сигналів", і що при проектуванні цифрових схем треба враховути затримки елементів схеми, а саме при перехідних процесах схеми. В порівнянні з ідеальною симуляції схеми на рис.2, ми отримали реальну симуляцію схеми при синтезі нашого проекту в конкретну CPLD чи FPGA на рис.4, рис.5, рис. 6 .